| Memory usage: Understanding the stack.<br>Find the flaw in this program                                                                              |                                                          |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|

| int x = 2;<br>int* foo(int y)                                                                                                                        | ompiler assigns a memory location.<br>stack              |  |  |  |

| int z;<br>z = y * x;<br>return &z<br>}                                                                                                               | les on the stack                                         |  |  |  |

| <pre>int main(void) {     int* result = foo(10);  }</pre>                                                                                            | program counter and copies of all registers on the stack |  |  |  |

| This program returns a pointer to a variable on<br>the stack. What if another procedure call occurs<br>before the returned pointer is de-referenced? |                                                          |  |  |  |

|                                                                                                                                                      | EECS 124, UC Berkeley: 4                                 |  |  |  |

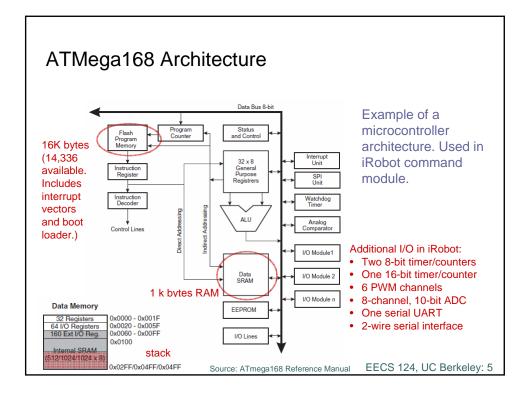

| Focus on<br>concurrency,<br>starting with<br>interrupts       Impute REFET (Reset Handler<br>(Record imp) REFET (Recet Handler)<br>(Record imp) Refet (Reference Mandler)<br>(Record imp) Refet (Refet (Reference Mandler)<br>(Record imp) Refet (Refet (Ref |                                                                              | The most typical an<br>ATmega168 is: | id general program se | tup for the Reset and Interrupt Vector Addresses in |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------|-----------------------|-----------------------------------------------------|--|--|

| concurrency,       jmp       EXT_INT0       ; IRQ0 Handler         concurrency,       0x0004       jmp       EXT_INT0       ; IRQ0 Handler         starting with       0x0064       jmp       PCINT0       ; PCINT0 Handler         interrupts       0x0064       jmp       PCINT1       ; IRQ0 Handler         0x0006       jmp       PCINT1       ; PCINT0 Handler         0x0006       jmp       PCINT2       ; PCINT2 Handler         0x0007       jmp       WDT       ; Watchdog Timer Handler         0x0012       jmp       TIM2_COMPB       ; Timer2 Compare & Handler         0x0012       jmp       TIM2_COMP       ; Source: ATmega168 Reference Manu<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              | Address Label                        | s Code                | Comments                                            |  |  |

| concurrency,<br>starting with<br>interrupts       imp       ET_INT1       i RQ1 Handler         0x0004       jmp       PCINT0       ; PCINT0 Handler         0x0006       jmp       PCINT2       ; PCINT0 Handler         0x0007       jmp       PCINT2       ; PCINT0 Handler         0x0008       jmp       PCINT2       ; PCINT0 Handler         0x0010       jmp       TIM_COMPB       ; Timer2 Compare & Handler         0x0012       jmp       TIM_COMPA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Focus on                                                                     |                                      | 2.2                   | ,                                                   |  |  |

| Concurrency,<br>starting with<br>interrupts       Imp       PCINTO       ; PCINTO Handler         0x0006       jmp       PCINT1       ; PCINTO Handler         0x0006       jmp       PCINT1       ; PCINTI Handler         0x0007       jmp       PCINT2       ; PCINT2 Handler         0x0008       jmp       PCINT2       ; PCINT2 Handler         0x0001       jmp       TIM2_COMPA       ; Timer2 Compare A Handler         0x0012       jmp       TIM2_COMPA       ; Timer2 Compare A Handler         0x0014       jmp       TIM2_COMPA       ; Timer2 Compare A Handler         0x0012       jmp       TIM2_COMPA       ; Timer2 Compare A Handler         0x0014       jmp       TIM2_COMPA       ; Timer2 Compare A Handler         0x014<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |                                      |                       |                                                     |  |  |

| starting with<br>interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CONCULLENCY                                                                  |                                      |                       |                                                     |  |  |

| starting with<br>interrupts       imp       pciNT2       ; pciNT2 Handler         0x000c       jmp       WDT       ; Matchdog Timer Handler         0x0010       jmp       TIM_COMPB       ; Timer2 Compare A Handler         0x0012       jmp       TIM_COMPB       ; Timer2 Compare B Handler         0x0013       jmp       TIM_COMPB       ; Timer2 Compare B Handler         0x0014       jmp       TIM_COMPB       ; Timer2 Compare B Handler         0x0013       jmp       TIM_COMPB       ; Timer2 Compare B Handler         0x0014       jmp       TIM_COMPA       ; Timer2 Compare B Handler         0x0014       jmp       TIM_COMPA       ; Timer2 Compare B Handler      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | concarrency,                                                                 |                                      | 2.02                  |                                                     |  |  |

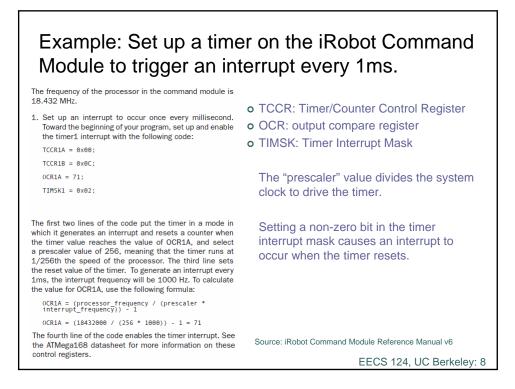

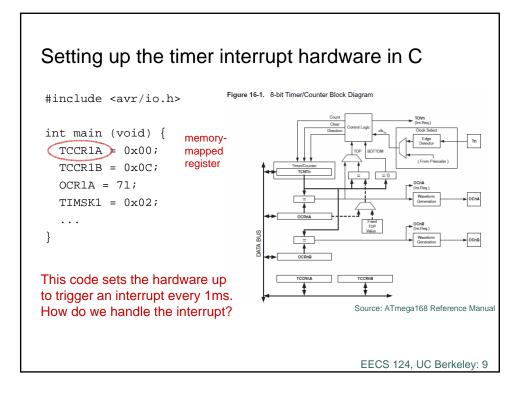

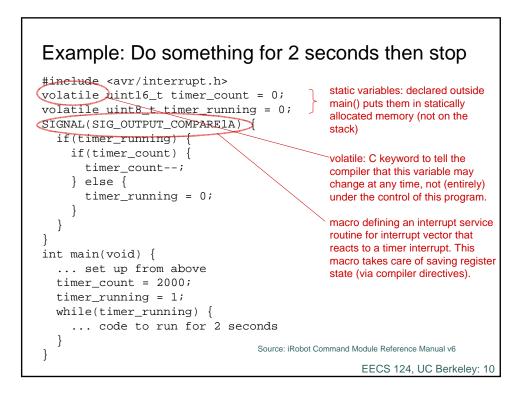

| interrupts       0x0000 jmp TIM_COMPA ; Timer2 Compare A Handler<br>0x0010 jmp TIM2_COMPB ; Timer2 Compare B Handler<br>0x0014 jmp TIM2_COMPB ; Timer2 Compare B Handler<br>0x0014 jmp TIM2_COMP ; Timer2 Compare B Handler         Triggers:       Source: ATmega168 Reference Manu         • A level change on an interrupt request pin       • Writing to an interrupt pin configured as an output ("software interrupt")         Responses:       • Disable interrupts.         • Push the current program counter onto the stack.         • Execute the instruction at a designated address in the flash memory.         Design of interrupt service routine:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | starting with                                                                |                                      |                       |                                                     |  |  |

| Interrupts       0x0010 jmp TIM_COMPB ; Timer2 Compare B Handler<br>0x0012 jmp TIM_COVP ; Timer2 Overflow Handler         Triggers:       Source: ATmega168 Reference Manu         • A level change on an interrupt request pin       • Writing to an interrupt pin configured as an output ("software interrupt")         Responses:       • Disable interrupts.         • Push the current program counter onto the stack.         • Execute the instruction at a designated address in the flash memory.         Design of interrupt service routine:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Starting with                                                                |                                      | J.12                  |                                                     |  |  |

| <ul> <li>imp TIM2_OVP ; Timer2 Overflow Handler<br/>0x0014 jmp TIM1_CAPT ; Timer1 Capture Handler</li> <li>Triggers: Source: ATmega168 Reference Manu</li> <li>A level change on an interrupt request pin</li> <li>Writing to an interrupt pin configured as an output ("software interrupt")</li> <li>Responses:         <ul> <li>Disable interrupts.</li> <li>Push the current program counter onto the stack.</li> <li>Execute the instruction at a designated address in the flash memory.</li> </ul> </li> <li>Design of interrupt service routine:</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                              | 0x000E                               | jmp TIM2_COMPA        | ; Timer2 Compare A Handler                          |  |  |

| <ul> <li>imp TIM2_OVP ; Timer2 Overflow Handler<br/>0x0014 jmp TIM1_CAPT ; Timer1 Capture Handler</li> <li>Triggers: Source: ATmega168 Reference Manu</li> <li>A level change on an interrupt request pin</li> <li>Writing to an interrupt pin configured as an output ("software interrupt")</li> <li>Responses:         <ul> <li>Disable interrupts.</li> <li>Push the current program counter onto the stack.</li> <li>Execute the instruction at a designated address in the flash memory.</li> </ul> </li> <li>Design of interrupt service routine:</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Interrupts                                                                   | 0x0010                               | jmp TIM2_COMPH        | ; Timer2 Compare B Handler                          |  |  |

| <ul> <li>Triggers: Source: ATmega168 Reference Manu</li> <li>A level change on an interrupt request pin</li> <li>Writing to an interrupt pin configured as an output ("software interrupt")</li> <li>Responses: <ul> <li>Disable interrupts.</li> <li>Push the current program counter onto the stack.</li> <li>Execute the instruction at a designated address in the flash memory.</li> </ul> </li> <li>Design of interrupt service routine:</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                            | 0x0012                               | jmp TIM2_OVF          | ; Timer2 Overflow Handler                           |  |  |

| <ul> <li>A level change on an interrupt request pin</li> <li>Writing to an interrupt pin configured as an output ("software interrupt")</li> <li>Responses:</li> <li>Disable interrupts.</li> <li>Push the current program counter onto the stack.</li> <li>Execute the instruction at a designated address in the flash memory.</li> <li>Design of interrupt service routine:</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                              | 0x0014                               | jmp TIM1_CAPT         | ; Timerl Capture Handler                            |  |  |

| <ul> <li>Disable interrupts.</li> <li>Push the current program counter onto the stack.</li> <li>Execute the instruction at a designated address in the flash memory.</li> </ul> Design of interrupt service routine:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | • Writing to an interrupt pin configured as an output ("software interrupt") |                                      |                       |                                                     |  |  |

| <ul> <li>Push the current program counter onto the stack.</li> <li>Execute the instruction at a designated address in the flash memory.</li> <li>Design of interrupt service routine:</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                              |                                      |                       |                                                     |  |  |

| <ul> <li>Execute the instruction at a designated address in the flash memory.</li> <li>Design of interrupt service routine:</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • Disable interrupts.                                                        |                                      |                       |                                                     |  |  |

| <ul> <li>Execute the instruction at a designated address in the flash memory.</li> <li>Design of interrupt service routine:</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ul> <li>Push the current program counter onto the stack</li> </ul>          |                                      |                       |                                                     |  |  |

| Design of interrupt service routine:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                              |                                      |                       |                                                     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • Execute the instruction at a designated address in the flash memory.       |                                      |                       |                                                     |  |  |

| <ul> <li>Re-enable interrupts before returning from interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                              |                                      |                       |                                                     |  |  |

| • The chapte interrupts before returning non-interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                              |                                      |                       |                                                     |  |  |

| EECS 124, UC Berkeley: 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                              |                                      |                       | EECS 124, UC Berkeley: 7                            |  |  |

## Summary

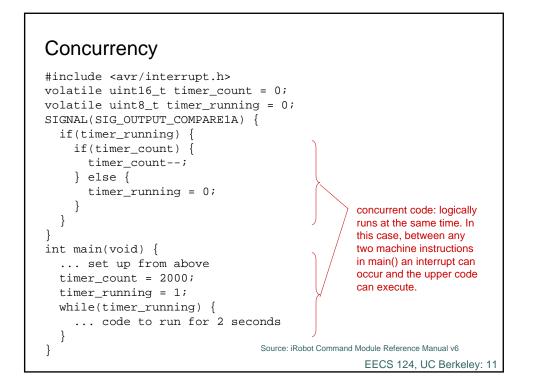

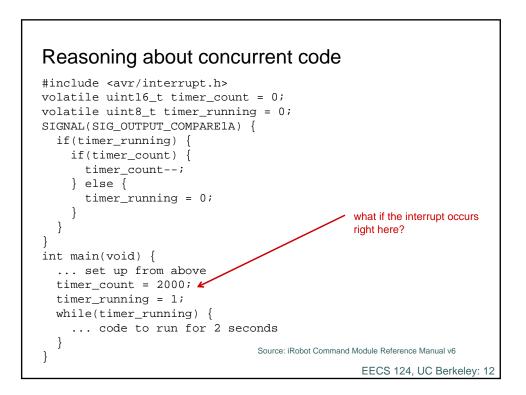

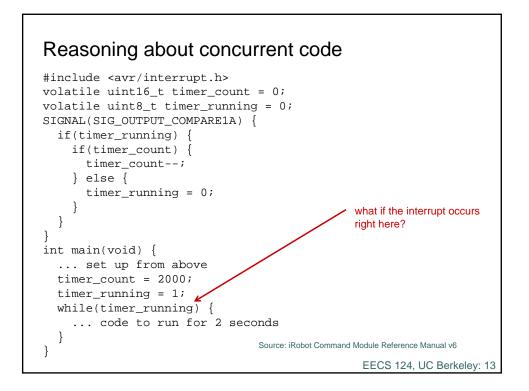

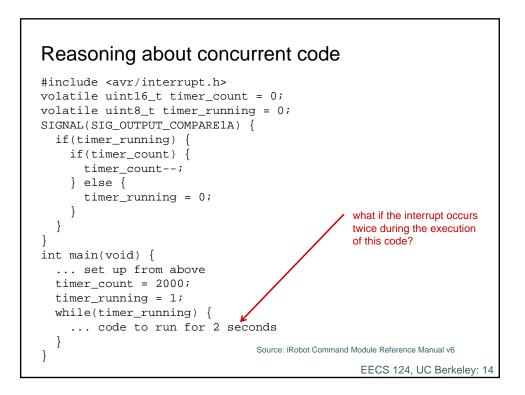

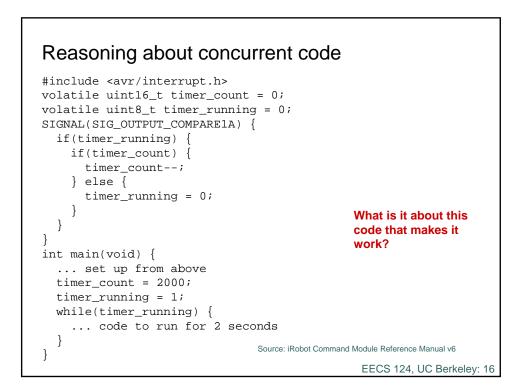

Interrupts introduce a great deal of nondeterminism into a computation. Very careful reasoning about the design is necessary.

EECS 124, UC Berkeley: 17